상품상세정보

▶ Academic Product

- 아카데믹 제품은 학교 지원 프로그램으로 일반 제품과 동일한 제품을 학교에 할인된 가격으로 판매하는 제품입니다.

- 할인된 가격으로 판매되는 아카데믹 제품은 일반 제품 구매와 달리 아래와 같은 아카데믹 정보를 제공해 주셔야합니다.

- 제품 주문결제 후 아래와 같은 아카데믹 정보(영문)를 sales@inipro.net으로 보내주시기 바랍니다.

- 학생 개인인 경우 학생정보와 함께 재학증명서 사본을 보내주시기 바랍니다.

- 아카데믹 정보 (※ 영문으로 정확하게 작성 부탁드립니다.)

- 학교 :

- 학과 :

- 담당교수 이름 :

- 담당교수 연구실 전화번호 :

- 담당교수 학교계정의 이메일 :

- 담당학생 이름 :

- 담당학생 연구실 전화번호 :

- 담당학생 학교계정의 이메일 :

▶ 실습교재 (별도구매)

▶ Overview

The DE1-SoC Development Kit presents a robust hardware design platform built around the Altera System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. Users can now leverage the power of tremendous re-configurability paired with a high-performance, low-power processor system. Altera’s SoC integrates an ARM-based hard processor system (HPS) consisting of processor, peripherals and memory interfaces tied seamlessly with the FPGA fabric using a high-bandwidth interconnect backbone. The DE1-SoC development board includes hardware such as high-speed DDR3 memory, video and audio capabilities, Ethernet networking, and much more.

The DE1-SOC Development Kit contains all components needed to use the board in conjunction with a computer that runs the Microsoft Windows XP or later ( 64-bit OS and Quartus II 64-bit are required to compile projects for DE1-SoC ).

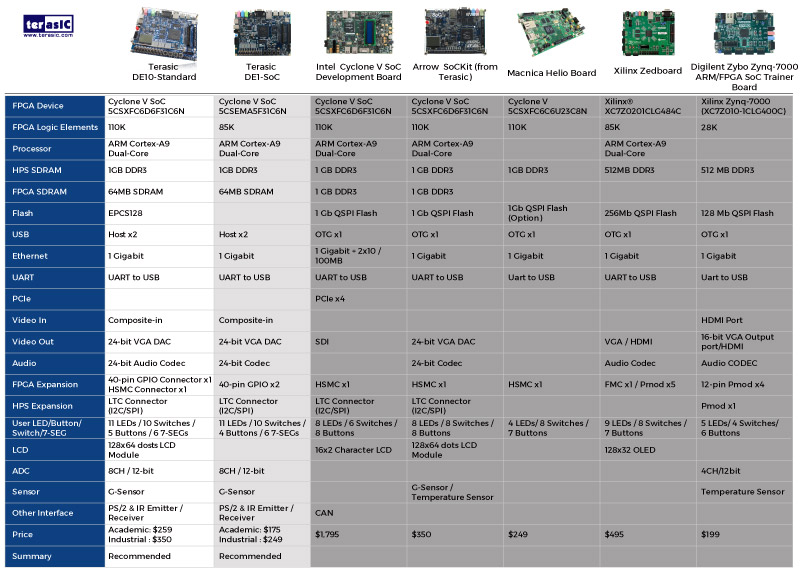

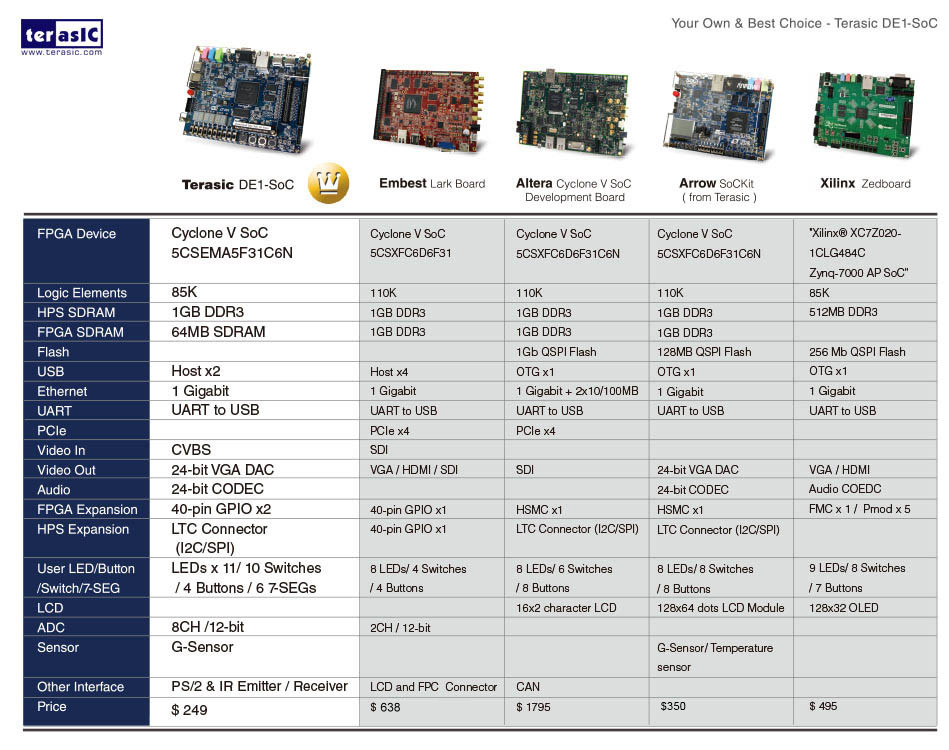

Board Comparisons

Component Solution for Altera FPGAs

| * Power Solution | * Memory Solution | * Clock Solution | * Ethernet Solution | |||

|  |  |  | |||

| * Inductive Component Solution | * Capacitive Component Solution | * ADC, Video, Accelerometer and Reset Generator Solution | ||||

|  |  |

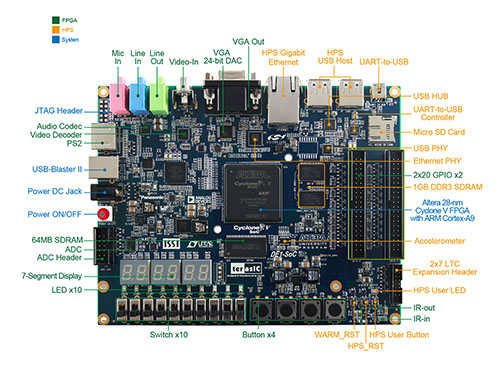

▶ Specification

The DE1-SoC board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects.

The following hardware is provided on the board:

FPGA Device

- Cyclone V SoC 5CSEMA5F31C6 Device

- Dual-core ARM Cortex-A9 (HPS)

- 85K Programmable Logic Elements

- 4,450 Kbits embedded memory

- 6 Fractional PLLs

- 2 Hard Memory Controllers

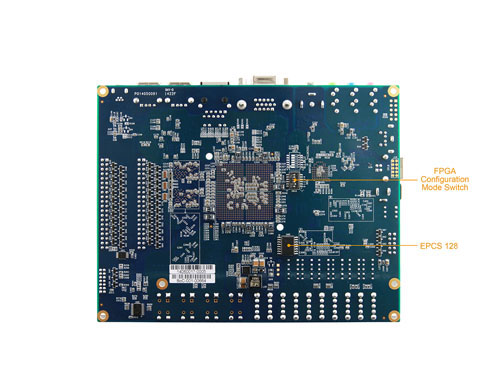

Configuration and Debug

- Serial Configuration device – EPCS128 on FPGA

- On-Board USB Blaster II (Normal type B USB connector)

Memory Device

- 64MB (32Mx16) SDRAM on FPGA

- 1GB (2x256Mx16) DDR3 SDRAM on HPS

- Micro SD Card Socket on HPS

Communication

- Two USB 2.0 Host Ports (ULPI interface with USB type A connector) on HPS

- UART to USB (USB Mini B connector)

- 10/100/1000 Ethernet

- PS/2 mouse/keyboard

- IR Emitter/Receiver

Connectors

- Two 40-pin Expansion Headers (voltage levels: 3.3V)

- One 10-pin ADC Input Header

- One LTC connector (One Serial Peripheral Interface (SPI) Master ,one I2C and one GPIO interface )

Display

- 24-bit VGA DAC

Audio

- 24-bit CODEC, Line-in, line-out, and microphone-in jacks

Video Input

- TV Decoder (NTSC/PAL/SECAM) and TV-in connector

ADC

- sample rate: 500 KSPS

- Channel number: 8

- Resolution: 12 bits

- Analog input range : 0 ~ 4.096 V

Switches, Buttons and Indicators

- 4 User Keys (FPGA x4)

- 10 User switches (FPGA x10)

- 11 User LEDs (FPGA x10 ; HPS x 1)

- 2 HPS Reset Buttons (HPS_RST_n and HPS_WARM_RST_n)

- Six 7-segment displays

Sensors

- G-Sensor on HPS

Power

- 12V DC input

Block Diagram of the DE1-SOC Board

▶ Resources

How to distinguish rev. B, rev. C, rev. D, rev. E, rev. F and rev G board?

Reference Book:

Modern Digital Designs with EDA, VHDL and FPGA

Documents

More resources about IP and Dev. Kit are available on Intel User Forums.

CD-ROM

( 64-bit OS and Quartus II 64-bit are required to compile projects for DE1-SoC )

BSP(Board Support Package) for Altera SDK OpenCL 18.1

BSP(Board Support Package) for Altera SDK OpenCL 16.0

BSP(Board Support Package) for Altera SDK OpenCL 14.0

Title Linux Kernel Size(KB) Date Added Download DE1-SoC OpenCL User Manual -- 2870 KB 2014-11-28

DE1-SoC OpenCL BSP(.zip) 3.12 84.2 MB 2015-01-28

DE1-SoC OpenCL BSP(.tar.gz) 3.12 84.2 MB 2015-01-28

| Title | Linux Kernel | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| DE1-SoC OpenCL User Manual | -- | 2870 KB | 2014-11-28 | |

| DE1-SoC OpenCL BSP(.zip) | 3.12 | 84.2 MB | 2015-01-28 | |

| DE1-SoC OpenCL BSP(.tar.gz) | 3.12 | 84.2 MB | 2015-01-28 |

Linux BSP (Board Support Package): MicroSD Card Image

Other course resources you might interested:

School: Cornell UniversitySenior Lecturer: Bruce Land

Course 1: - ECE5760 Advanced Microcontroller Design and system-on-chip [DE2]

School: Cornell UniversitySenior Lecturer: Bruce Land

Course 1: - ECE5760 Advanced Microcontroller Design and system-on-chip [DE2]

▶ Compare

※ For more details, plesae click the picture ※

▶ Demo

*If the film is unavailable, please kindly try another link below:

▶ Kit Contents

배송안내

● 이니프로에서 판매하는 모든 제품은 이니프로에서 통관 처리후 우체국 택배로 배송됩니다.

● 국내재고가 있는 경우 결제일로부터 3~4 영업일 안에 국내재고가 없는 경우 결제일로부터 3주 안에 배송됩니다.

● 현재 국내재고가 있는지 확인하시려면 1:1 문의 게시판에 남겨주시거나 sales@inipro.net 으로 메일을 보내주시기 바랍니다.

● 제조사 재고가 부족하여 3주 안에 배송이 어려울 경우 메일로 안내해 드리니 참고하시기 바랍니다.

교환 및 반품안내

● 제품 수령후 7일이내에 이니프로 고객센터에 연락하여 교환 및 반품 처리 요청하면 교환 가능합니다.

● 제품은 박스 상단에 아이디 또는 성함 등을 표기한 후 쇼핑몰 하단의 주소 및 연락처로 택배 발송해 주시기 바랍니다.

● 제품 및 제품포장 박스 등에 손상된 부분이 없는지 고객센터에서 확인한 후 교환 및 반품 처리됩니다.

환불안내

● 제품 수령후 7일이내에 이니프로 고객센터에 연락하여 환불 요청하면 환불 가능합니다.

● 제품은 박스 상단에 아이디 또는 성함 등을 표기한 후 쇼핑몰 하단의 주소 및 연락처로 택배 발송해 주시기 바랍니다.

● 제품 및 제품포장 박스 등에 손상된 부분이 없는지 고객센터에서 확인한 후 환불수수료(5천원+판매가의1%)을 제외한 나머지 금액을 환불 처리해 드립니다.

AS안내

● 제품 보증 기간이 90일인 제품입니다.

● 납품후 90일 이내에는 무상 AS, 90일 이후에는 유상 AS 처리됩니다.

장바구니 담기

상품이 장바구니에 담겼습니다.

바로 확인하시겠습니까?

찜 리스트 담기

상품이 찜 리스트에 담겼습니다.

바로 확인하시겠습니까?