상품상세정보

▶ Overview

The Altera® Stratix® V GX Transceiver Signal Integrity (SI) Development Kit provides a platform for electrical compliance testing and interoperability analysis. The accessibility to multiple channels allows for real-world analysis as implemented in the system with transceiver channels available through SMA and popular backplane connectors. You can use this development kit to perform the following tasks:

- Evaluate transceiver link performance from 600 Mbps to 12.5 Gbps

- Generate and check pseudo-random binary sequence (PRBS) patterns via a simple to use GUI (does not require the Quartus® II software)

- Access advanced equalization to fine tune link settings for optimal bit error ratio (BER)

- Perform jitter analysis

- Verify physical medium attachment (PMA) compliance to 10GbE, 10GBASE-KR, PCI Express® (PCIe®)(Gen1, Gen2, and Gen3), Serial RapidIO®, Gigabit Ethernet, 10-Gigabit Ethernet XAUI, Common Electrical I/O (CEI) 6G, CEI-11G, high-definition serial digital interface (HD-SDI), Interlaken, and other major standards

- Use the built-in high speed backplane connectors to evaluate custom backplane performance and evaluate link BER

▶ Specification

Featured device

- 5SGXEA7N2F40C2N

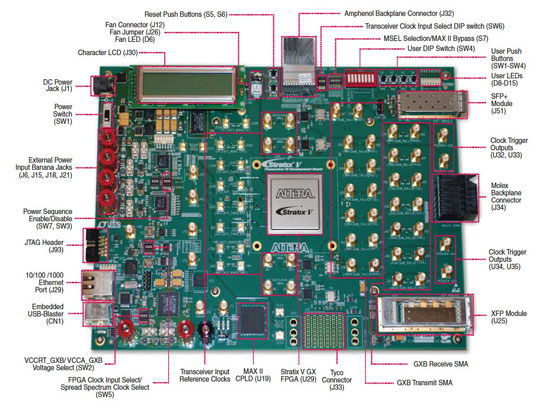

Configuration status and set-up elements

- JTAG

- On-board USB-BlasterTM

- Fast passive parallel (FPP) configuration via MAX® II device and flash memory

- Two configuration file storage

- Temperature measurement circuitry (die and ambient temperature)

Clocks

- 50 MHz, 125 MHz, programmable oscillators (preset values: 624 MHz, 644.5 MHz, 706.25 MHz, and 875 MHz)

- SMA connectors for supplying an external differential clock to transceiver reference clock

- SMA connectors for supplying an external differential clock to the FPGA fabric

- SMA connectors to output a differential clock from the FPGA's phase-locked loop (PLL) output pin

General user input/output

- 10-/100-/1000-Mbps Ethernet PHY (RGMII) with RJ-45 (copper) connector

- 16x2 character LCD

- One 8-postion dipswitch

- Eight user LEDs

- Four user pushbuttons

Memory devices

- 128-megabyte (MB) sync flash memory (primarily to store FPGA configurations)

High speed serial interfaces

- Seven full-duplex transceiver channels routed to SMA connectors

- Short trace routed on a micro-strip

- Six strip-line channels from the with all the trace lengths are matched across channels

- 21 full-duplex transceiver channels routed to backplane connector

- Seven channels to Molex® Impact® connector

- Seven channels to Amphenol® XCede®

- Seven channels to footprint of Tyco Strada® Whisper® (connector is not populated)

Power

- Laptop DC input

- Voltage margining

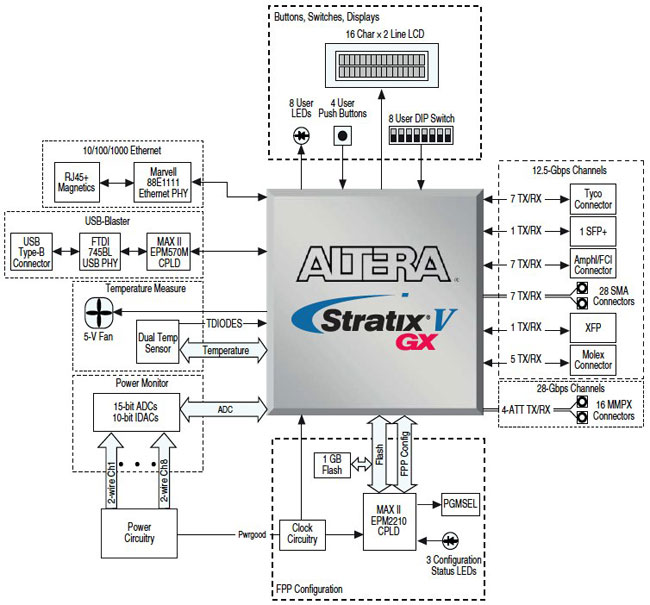

Stratix V GX Transceiver Signal Integrity Development Board Block Diagram

▶ Layout

▶ Resources

Documents

CD-ROM

▶ Kit Contents

- Altera's Complete Design Suite (download from Altera download center )

- Quartus II software includes support for Stratix V FPGAs

- 1-year license included

- Nios® II Embedded Design Suite

- MegaCore® intellectual property (IP) library includes PCIe, Triple-Speed Ethernet, Serial Digital Interface (SDI), and DDR3 SDRAM High-Performance Controller MegaCore IP cores

- IP evaluation available through OpenCore Plus

- Board Update Portal

- Featuring Nios II web server and remote system update

- GUI-based Board Test System

- Interfaces to PC via JTAG

- User controllable PMA settings (pre-emphasis, equalization, and so on)

- Status indication (errors, BER, and so on)

- Complete documentation

- User guide

- Reference manual

- Board schematics and layout design files

배송안내

● 이니프로에서 판매하는 모든 제품은 이니프로에서 통관 처리후 우체국 택배로 배송됩니다.

● 국내재고가 있는 경우 결제일로부터 3~4 영업일 안에 국내재고가 없는 경우 결제일로부터 3주 안에 배송됩니다.

● 현재 국내재고가 있는지 확인하시려면 1:1 문의 게시판에 남겨주시거나 sales@inipro.net 으로 메일을 보내주시기 바랍니다.

● 제조사 재고가 부족하여 3주 안에 배송이 어려울 경우 메일로 안내해 드리니 참고하시기 바랍니다.

교환 및 반품안내

● 제품 수령후 7일이내에 이니프로 고객센터에 연락하여 교환 및 반품 처리 요청하면 교환 가능합니다.

● 제품은 박스 상단에 아이디 또는 성함 등을 표기한 후 쇼핑몰 하단의 주소 및 연락처로 택배 발송해 주시기 바랍니다.

● 제품 및 제품포장 박스 등에 손상된 부분이 없는지 고객센터에서 확인한 후 교환 및 반품 처리됩니다.

환불안내

● 제품 수령후 7일이내에 이니프로 고객센터에 연락하여 환불 요청하면 환불 가능합니다.

● 제품은 박스 상단에 아이디 또는 성함 등을 표기한 후 쇼핑몰 하단의 주소 및 연락처로 택배 발송해 주시기 바랍니다.

● 제품 및 제품포장 박스 등에 손상된 부분이 없는지 고객센터에서 확인한 후 환불수수료(5천원+판매가의1%)을 제외한 나머지 금액을 환불 처리해 드립니다.

AS안내

● 제품 보증 기간이 90일인 제품입니다.

● 납품후 90일 이내에는 무상 AS, 90일 이후에는 유상 AS 처리됩니다.

장바구니 담기

상품이 장바구니에 담겼습니다.

바로 확인하시겠습니까?

찜 리스트 담기

상품이 찜 리스트에 담겼습니다.

바로 확인하시겠습니까?